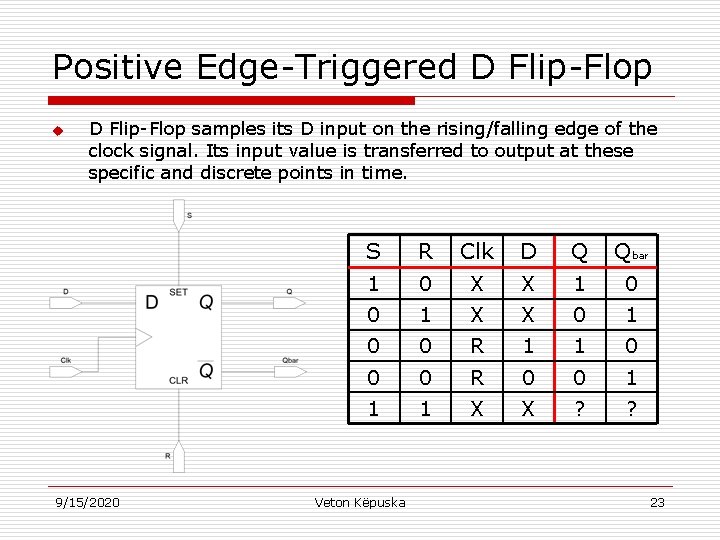

Digital frequency doubler with a dual edge triggered flip flop in VHDL. 8.2.7 Registers and Latches in VHDL Register and latch circuits can be specified using structural VHDL. Something like this:if (risingedge (sig1)) then bit < '0' elsif (risingedge (sig2)) then bit < '1' end if D. Use positive edge triggered D flip-flop (shown in the below figure) to design the circuit. Flip-Flop triggered on the edge of two signals. of all edge-triggered flip-flops contain essential hazards, which can be masked only by controlling path delays, difficult in a PLD-based design. I need a flip flop that reacts on the edges of two different signals. When it reaches 1111, it should revert back to 0000 after the next edge.

About … icon-addNote android4 Answer apple4 icon-appStoreEN icon-appStoreES icon-appStorePT icon-appStoreRU Imported Layers Copy 7 icon-arrow-spined icon-ask icon-attention icon-bubble-blue icon-bubble-red ButtonError ButtonLoader ButtonOk icon-cake icon-camera icon-card-add icon-card-calendar icon-card-remove icon-card-sort chrome-extension-ru chrome-extension-es-mx chrome-extension-pt-br chrome-extension-ru comment comment icon-cop-cut icon-cop-star Cross Dislike icon-editPen icon-entrance icon-errorBig facebook facebook-logo flag flag_vector icon-globe google-logo icon-googlePlayEN icon-googlePlayRU icon-greyLoader icon-cake Heart 4EB021E9-B441-4209-A542-9E882D3252DE Created with sketchtool. The circuit shown is triggered on the leading edge of the switch, so output changes when switch is once pressed. Design a circuit for an edge triggered 4-bit binary up counter (0000 to 1111).

0 kommentar(er)

0 kommentar(er)